# Memory Systems

CH008

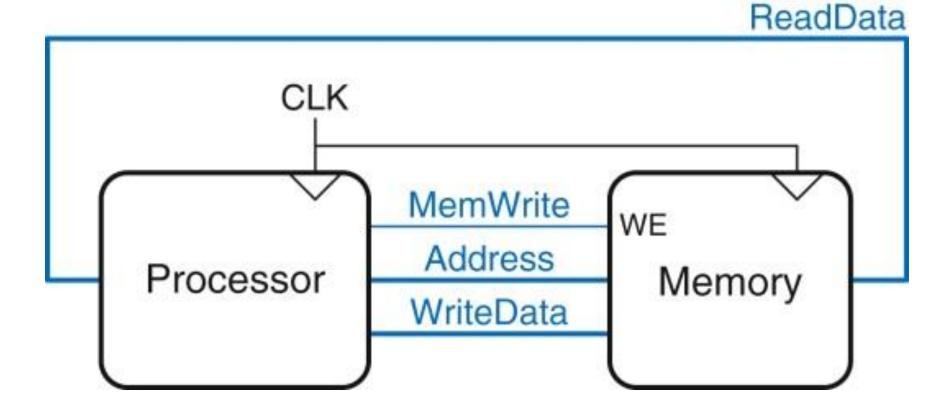

Figure 8.1 The memory interface

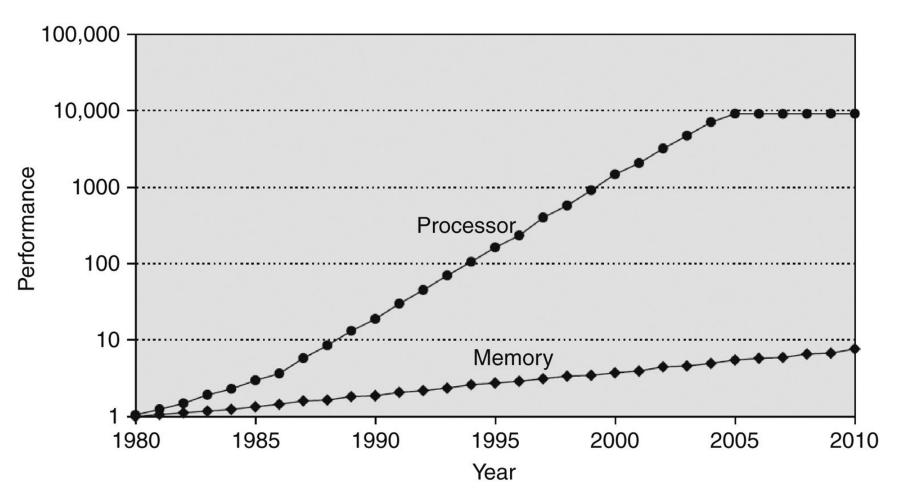

Figure 8.2 Diverging processor and memory performance. Adapted with permission from Hennessy and Patterson, *Computer Architecture: A Quantitative Approach*, 5th ed., Morgan Kaufmann, 2011.

Copyright © 2016 Elsevier Ltd. All rights reserved.

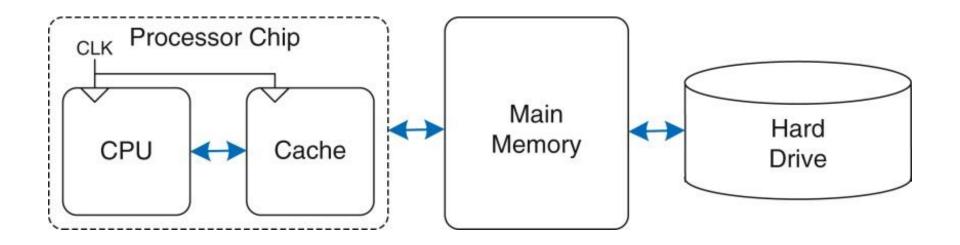

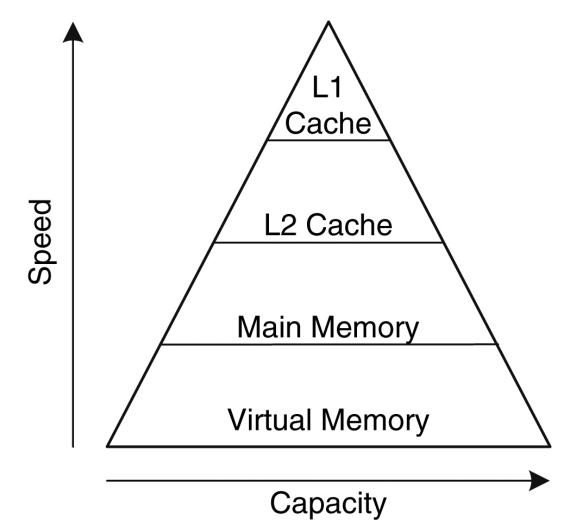

Figure 8.3 A typical memory hierarchy

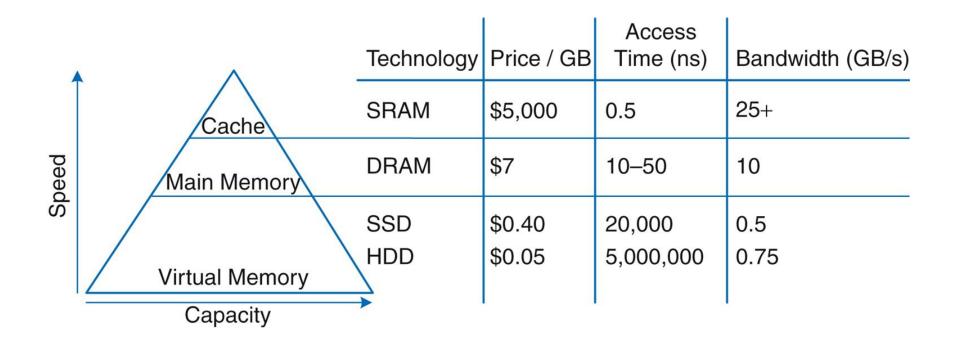

Figure 8.4 Memory hierarchy components, with typical characteristics in 2015

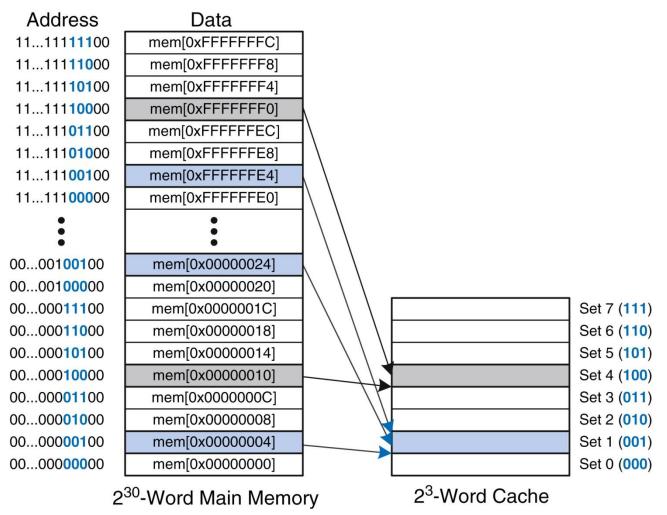

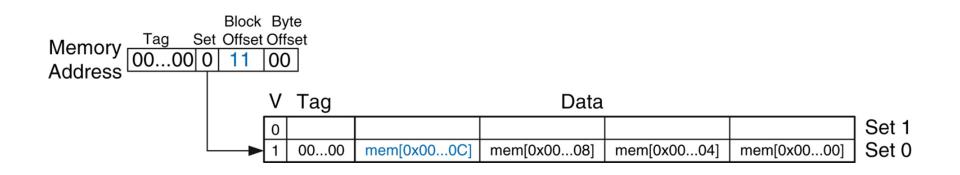

### Figure 8.5 Mapping of main memory to a direct mapped cache

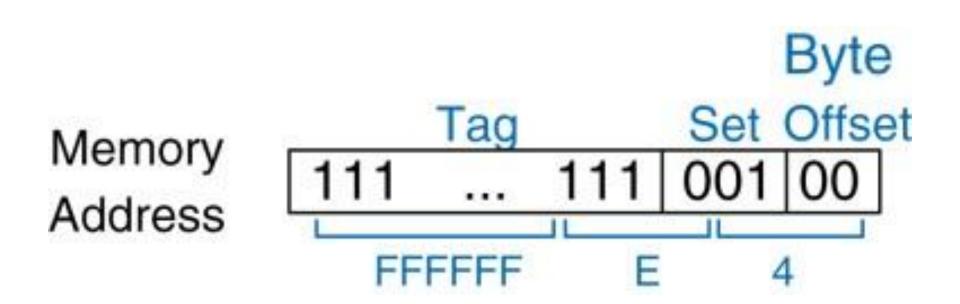

# Figure 8.6 Cache fields for address 0xFFFFFE4 when mapping to the cache in Figure 8.5

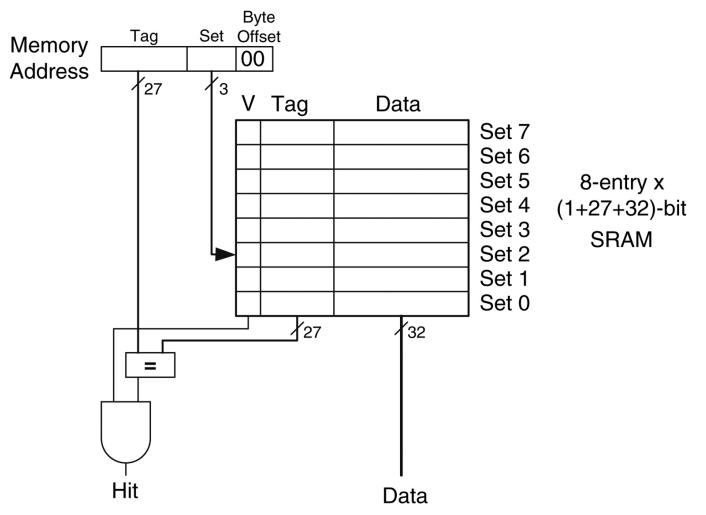

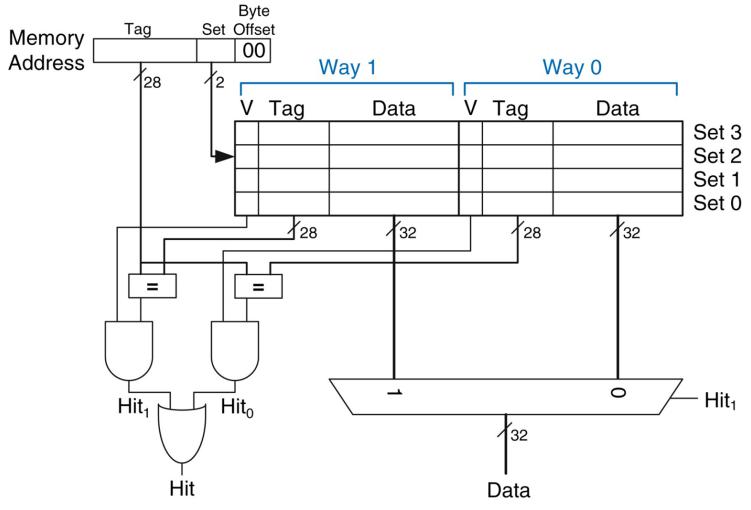

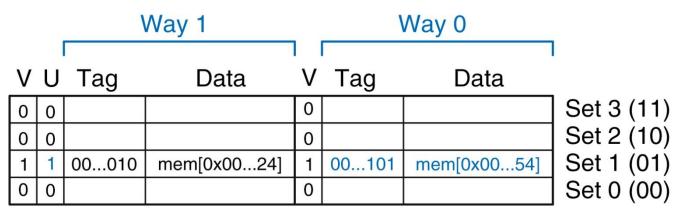

### Figure 8.9 Two-way set associative cache

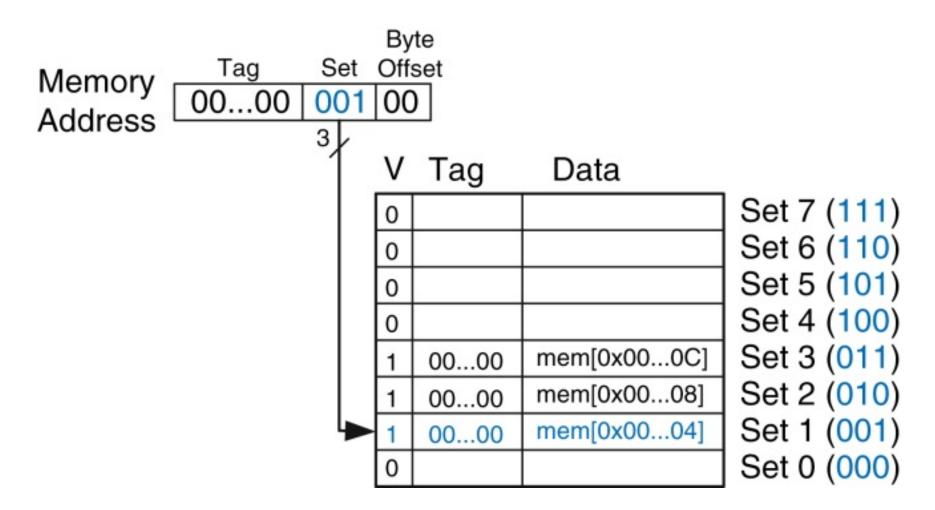

#### Figure 8.10 Two-way set associative cache contents

## Figure 8.11 Eight-block fully associative cache

|   | Way | 17   |   | Way | 6    |   | Way | 5    |   | Way | 4    |   | Way | 3    |   | Way | 2    |   | Way | 1    |   | Way | 0    |

|---|-----|------|---|-----|------|---|-----|------|---|-----|------|---|-----|------|---|-----|------|---|-----|------|---|-----|------|

| V | Tag | Data |

|   |     |      |   |     |      |   |     |      |   |     |      |   |     |      |   |     |      |   |     |      |   |     |      |

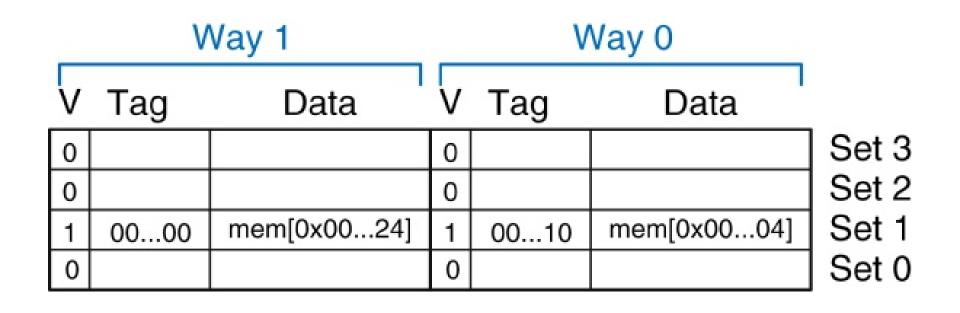

### Figure 8.12 Direct mapped cache with two sets and a four-word block size

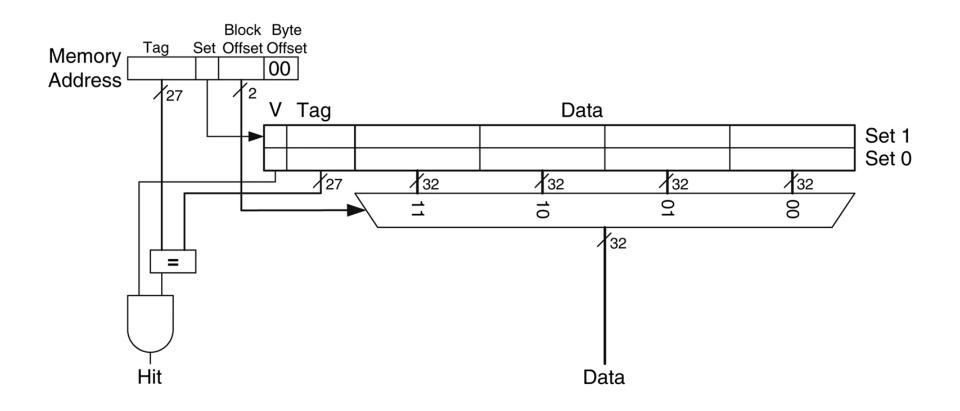

# Figure 8.13 Cache fields for address 0x8000009C when mapping to the cache of Figure 8.12

#### Figure 8.14 Cache contents with a block size *b* of four words

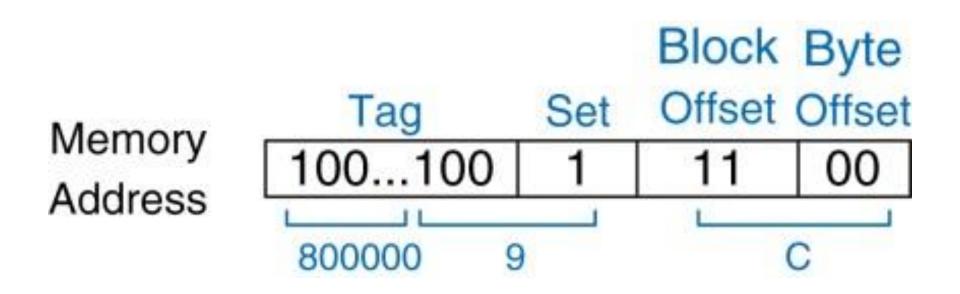

Figure 8.15 Two-way associative cache with LRU replacement

|   |   | \     | Way 1       |   |       |             |            |

|---|---|-------|-------------|---|-------|-------------|------------|

| V | U | Tag   | Data        | V | Tag   | Data        | l          |

| 0 | 0 |       |             | 0 |       |             | Set 3 (11) |

| 0 | 0 |       |             | 0 |       |             | Set 2 (10) |

| 1 | 0 | 00010 | mem[0x0024] | 1 | 00000 | mem[0x0004] | Set 1 (01) |

| 0 | 0 |       |             | 0 |       |             | Set 0 (00) |

(a)

(b)

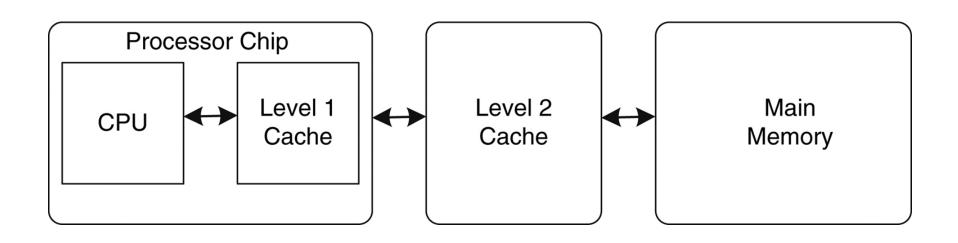

Figure 8.16 Memory hierarchy with two levels of cache

Copyright © 2016 Elsevier Ltd. All rights reserved.

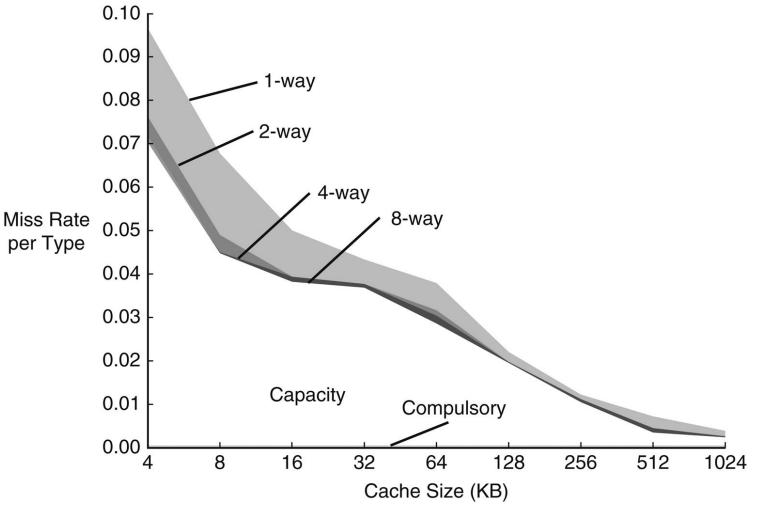

Figure 8.17 Miss rate versus cache size and associativity on SPEC2000 benchmark. (Adapted with permission from Hennessy and Patterson, *Computer Architecture: A Quantitative Approach*, 5th ed., Morgan Kaufmann, 2012.)

Copyright © 2016 Elsevier Ltd. All rights reserved.

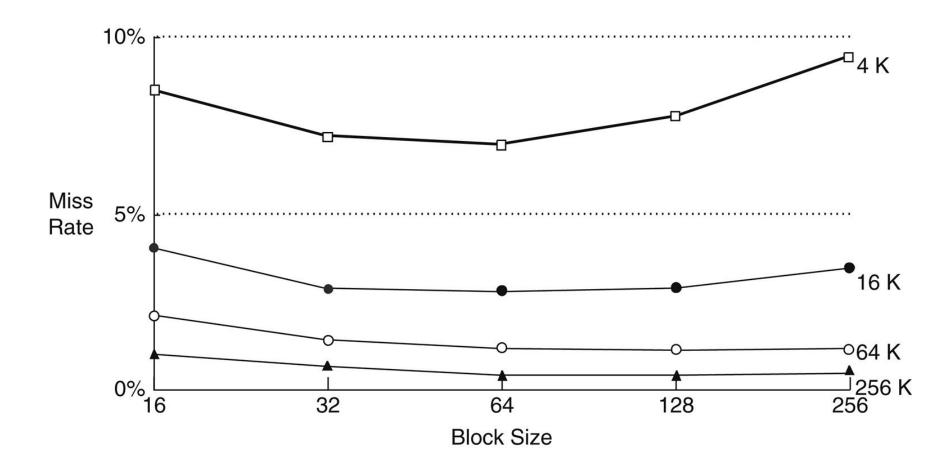

Figure 8.18 Miss rate versus block size and cache size on SPEC92 benchmark. (Adapted with permission from Hennessy and Patterson, *Computer Architecture: A Quantitative Approach*, 5th ed., Morgan Kaufmann, 2012.)

## Figure 8.19 Hard disk

Copyright  $\ensuremath{\mathbb{C}}$  2016 Elsevier Ltd. All rights reserved.

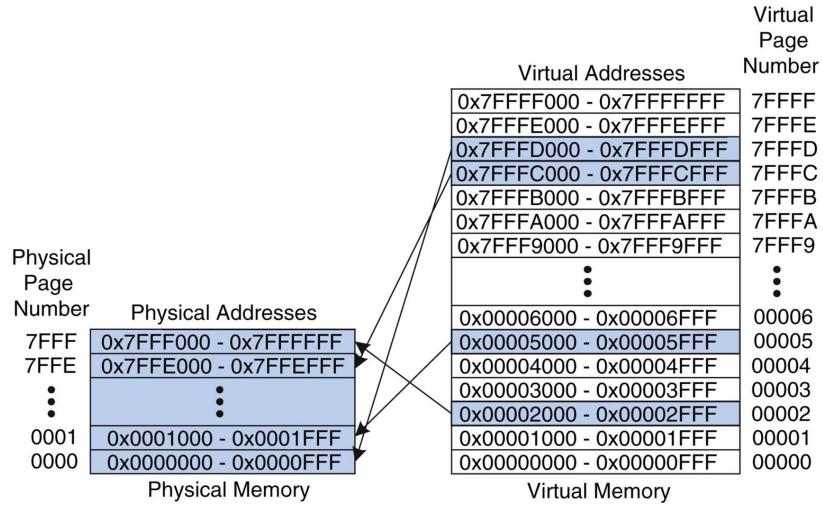

Figure 8.20 Virtual and physical pages

## Figure 8.21 Physical and virtual pages

Copyright © 2016 Elsevier Ltd. All rights reserved.

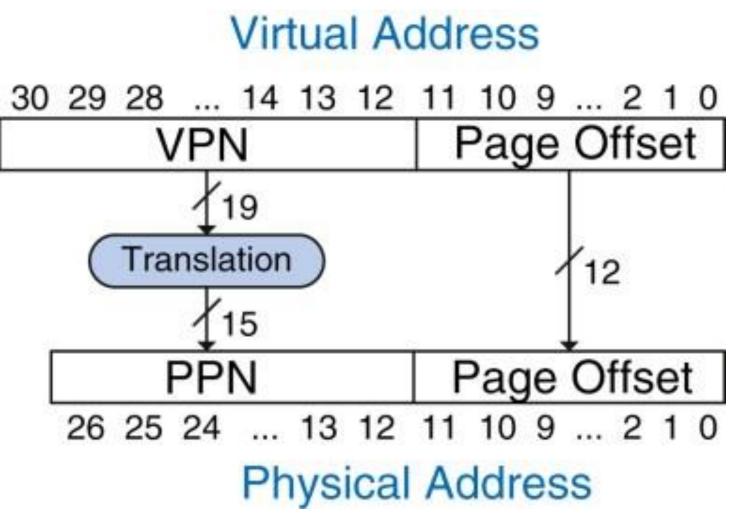

Figure 8.22 Translation from virtual address to physical address

| V | Physical<br>Page<br>Number | Virtual<br>Page<br>Number |

|---|----------------------------|---------------------------|

| 0 |                            | 7FFFF                     |

| 0 |                            | 7FFFE                     |

| 1 | 0x0000                     | 7FFFD                     |

| 1 | 0x7FFE                     | 7FFFC                     |

| 0 |                            | 7FFFB                     |

| 0 |                            | 7FFFA                     |

|   | •<br>•                     | •                         |

| 0 |                            | 00007                     |

| 0 |                            | 00006                     |

| 1 | 0x0001                     | 00005                     |

| 0 |                            | 00004                     |

| 0 |                            | 00003                     |

| 1 | 0x7FFF                     | 00002                     |

| 0 |                            | 00001                     |

| 0 |                            | 00000                     |

|   | Page Table                 |                           |

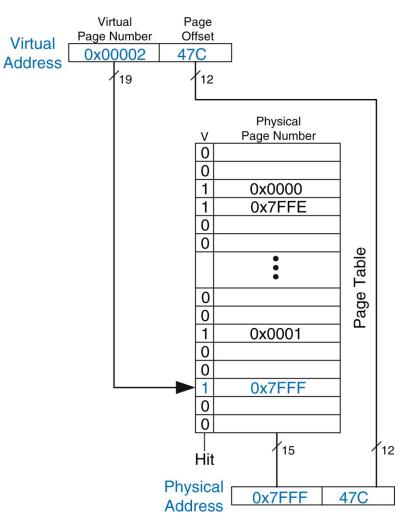

## Figure 8.24 Address translation using the page table

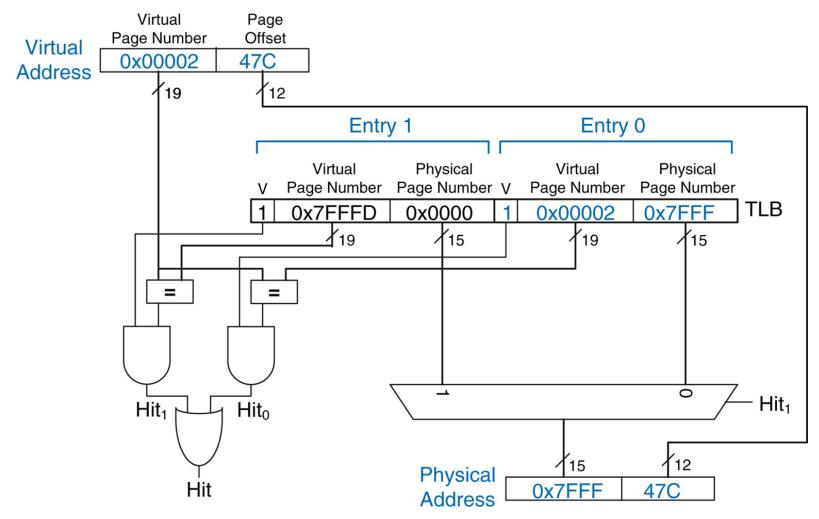

#### Figure 8.25 Address translation using a two-entry TLB

Copyright © 2016 Elsevier Ltd. All rights reserved.

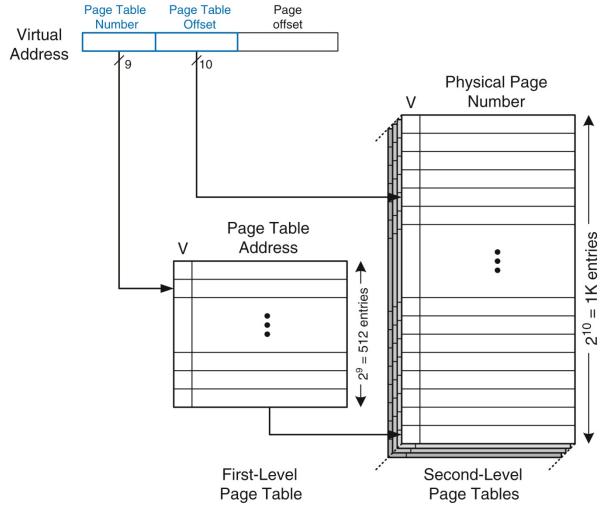

## Figure 8.26 Hierarchical page tables

Copyright © 2016 Elsevier Ltd. All rights reserved.

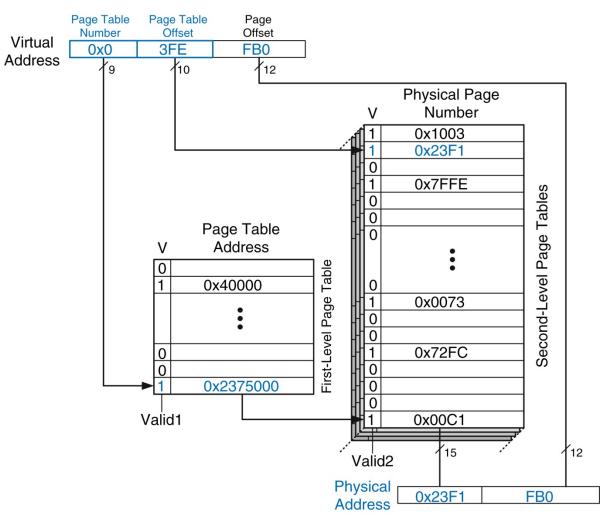

#### Figure 8.27 Address translation using a two-level page table

Copyright © 2016 Elsevier Ltd. All rights reserved.

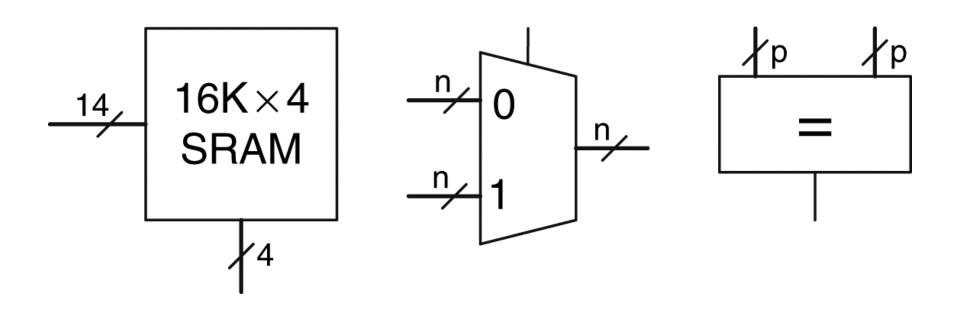

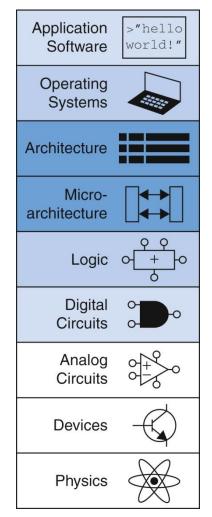

Figure 8.28 Building blocks

Figure 8.29 Computer system

Copyright © 2016 Elsevier Ltd. All rights reserved.

Copyright © 2016 Elsevier Ltd. All rights reserved.

## Fig u08-01

Copyright © 2016 Elsevier Ltd. All rights reserved.